- Views: 1K

- Replies: 1

Signal Name for Motherboard Manufacturers:

List of some common signal names of Wistron Board Manufacturer:| Signal Name | Description |

| CK-PWRGD | After the South Bridge receiving VRMPWRGD, sent this signal as high level for opening the clock. |

| G792-RST# | The high level s4end by the temperature control chip when the temperature is normal. |

| CLK_EN# | After CPU power supply being normal, send the low level that can be used to open the clock. |

| LID_CLOSE# | Close cover switch. |

| KBC-PWR-BTN# | Press the on/off switch to produce the trigger signal to EC. |

| AD_IN# , AC_IN# | The power adapter detection signal to EC, the low level represents that the adapter is inserted. |

| +5VALM, +3VALM | The standby power supply of South Bridge. |

| PWR-S5-EN | A control signal used to open standby voltage of South Bridge. |

| ACAV-IN | Power adapter detection output for charging chip. |

| ACIN | Power adapter detection input for charging chip. |

| DCIN | Power supply input for charging chip. |

| +3VL | 3.3V linear power supply, supply voltage to EC. |

| DCBATOUT | Common point. |

| AD+ | The first voltage that the power adapter converts. |

List of some common signal names of Inventec:

| Signal Name | Description |

| +VADP | Power adapter voltage. |

| ADP_EN# | Power adapter enable signal; Active low level. |

| ADP_PRES | Adapter detection output voltage. |

| +VBATR | Common point voltage. |

| +3VAL, +5VAL | Linear power supply. |

| PWR_SWIN_3# | The signal sent by trigger switch to EC chip. |

| KBC_PW_ON | The power signal; It is sent by EC after EC receiving trigger switch; It is use to open the system standby power supply under the battery mode (backup battery). |

| OCP | Over-current protection. |

| LIMIT_SIGNAL | The power adapter connector intermediate pin; Power identification signal. |

| +V3A, +V5A | Power supply of standby system. |

| VCCI_POR#3 | The initial reset signal of EC. |

List of some common signal names of Compal Manufacturer:

| Signal Name | Description |

| SUS_STAT# | Sent by the South Bridge; The low level indicates that the system will be in power-down (save power) mode. |

| BCLK | The front side bus clock signal. |

| ICH_POK | PWROS for the South Bridge; Inform the South Bridge system voltage power good. |

| VGATE | CPU core voltage power-good signal. |

| +CPU_CORE | CPU core voltage. |

| +VCCP | The working voltage of CPU front side bus; This voltage distributes in CPU, the North Bridge, and the South Bridge. |

| SUSP# | S0 voltage open signal. |

| SYSON | S3 voltage open signal. |

| PBTNOUT# | The boot trigger signal sent by EC to the South Bridge. |

| ON/OFF# | The trigger signal sent by boot trigger circuit to EC. |

| ON/OFFBTN# | Press power on key signal. |

| +3VALW, +5VALW | Inserting the adapter, that is the opened voltage. |

| VL | 5V linear power supply. |

| PACIN | The detection output signal is inserted to the adapter. |

| B+ | Common point voltage. |

List of some common signal names of Apple:

| Signal Name | Description |

| ONEWIRE_EN | ONEWIRE enable signal; For the adapter to identify circuit (the power connector LED green light). |

| ACPRN | Low level ACPRN signal sent by charging chip after the adapter is detected. |

| SMC_BATT_CHG_EN | The charging enable signal sent by SMC; Active-high level. |

| SMC_ADAPTER_EN | The high-level signal output by SMC after receiving the adapter detection signal. |

| SMC_BC_ACOK | The Adapter detection signal; Active – high level. |

| VR_PWRGD_CK505_L | The lower level signal of open clock; After CPU power supply chip generating CPU voltage normally, it will send the low level signal to open clock. |

| VR_PWRGOOD_DELAY | The power good signal sent by CPU power supply after generating CPU voltage normally and it will delay to send the power-good. |

| ALL_SYS_PWRGD | Convergence from all power supply good signal except CPU power supply |

| 1V8S3_RUNSS | S3 state voltage (memory supply) of 1.8V open signal. |

| PM_BATLOW_L | The indicator signal of low battery voltage; Active-low level. |

| =PPBUSA_G3H | Common point voltage. |

| PP3V3_G3_SB_RTC | 3.3V power supply of the South Bridge RTC circuit. |

| =PP3V3_S5_REG | 3.3V power supply in the condition of S5 provided the standby voltage to the South Bridge and others. |

| =PP3V42_G3H_REG | 3.42V power supply in the condition of G3 equivalent to the linear power supply of other machine. |

List of some common signal names of Quanta:

| Signal Name | Description |

| NBSWON# | Trigger signal for power on; Press the power on key to produce high-lowhigh signal to EC. |

| D/C# | Inverse relationship with ACIN (Just for motherboard with D/C# signal, where the motherboard is without BL/C# signal). |

| BL/C# | Represents high level, low battery (only for battery mode). |

| CPURST# | CPU reset signal; The North Bridge sent CPURST# to CPU after received PLTRST#. |

| PCIRST# | The PCI reset; Used for resetting the device on the PCI bus when powered on. |

| PLTRST# | The platform reset signal; After the South Bridge sending CPUPWRGD signal, through the delay buffer sent PLTRST# |

| CPUPWRGD | In the South Bridge internal, PWROK pin and VRMPWRGD pin signal through the logic generated CPUPWRGD. |

| CK_PWRGD | The South Bridge sent CL-PWRGD open clock chip after receiving VRMPWRGD. |

| VR-PWRGD-CK410# | CPU core voltage power managed the clock open signal from chip; Active low level. |

| DELAY_VR_PWG | CPU core voltage power-good signal. |

| PWROK_EC | After EC received high level HWPG signal, delay producing the PWROK_EC signal. |

| HWPG | By the PG Logic and all power supply except the CPU core power supply. |

| VR_ON | The CPU core voltage opening signal sent by EC. |

| MAINON | After EC receiving SLP_S3# from the South Bridge, after that producing S3 voltage opening signal. |

| SUSON | After EC receiving SLP_S5# from the South Bridge, then producing S3 voltage opening signal. |

| S5_ON | The opening signal of the South Bridge standby voltage sent by EC; Its use to convert the PCU to voltage S5. |

| SLP_S3#, SLP_S4# | ACPI controller signal sent by the South Bridge is used to opening voltage when the power is turned on, and it also used to shutting off voltage when the power is turned off. |

| DNBSWON# | EC sent high-low-high effective trigger signal to the South Bridge PWRBTN#. |

| +3VSUS, +5VSUS | The voltage under the condition of S3; Memory power supply; Sent by EC and opened by SUSON. |

| 3V_S5 | The voltage under the condition of S5. |

| +3VPCU, +5VPCU | EC Standby power supply |

| 3V_AL, 5V_AL, VL | 3V, 5V Linear power supply |

| ACIN, ACOK | Power Adapter detection |

| VIN | The common point voltage |

List of some common signal names of ASUS:

| Signal Name | |

| OTP_RESET# | CPU over temper |

| HW_PROTECT# | CPU over temper |

| FORCE_OFF# | The forced shutd voltage protectio |

| KBCRSM | The keyboard wa |

| LID_KBC# | The close-lid slee |

| LID_SW# | Close-lid sleep sw this signal is low |

| GATE_PWR_SW# | The booth trigge |

| H_CPURST# | The North Bridge PLTRST# signal. |

| PM_PWROK | After receiving A PW_PWROK. |

| CLK_PWRGD | The South Bridge receiving VRMPW |

| EC_CLK_EN | EC sent VRMPWR South Bridge tha |

| CPU_VRON | EC delayed 99ms For opening CPU |

| ALL_SYSTEM_PWRGD | Generated by me bus power supply signal logic. |

| SUSB_ON, SUSB#_PWR | S0 voltage open s |

| SUSC_ON, SUSC_PWR | S3 voltage open s |

| PM_PWRBTN# | After receiving PW effective trigger t |

| PWRSW_EC# | Laptop boot-up t |

| PM_RSMRST# | The reset signal o understood that normal when rec |

| SUS_PWRGD | SUS voltage pow |

| VSUS_ON | SUS voltage open signal. |

| +3VSUS | +3VO renamed to +3VSUS after jumper. |

| +5VSUS | +5VO renamed to +5VSUS after jumper. |

| +3VO | 3V standby voltage in S5dormant state. |

| +5VO | 5V standby voltage in S5dormant state. |

| +3VA_EC | +3VA renamed to +3VA_EC after through the inductance; As the EC standby power supply. |

| +3VA | +3VAO renamed to +3VA after jumper JP8101. |

| +5VA | +5VAO renamed to +5VA after jumper. |

| +3VAO | 3V linear voltage. |

| +5VAO | 5V linear voltage. |

| ACIN | Power adapter detection. |

| AC_BAT_SYS | The common point voltage. |

List of some common signal names of Dell:

| Signal Name | Signal Name |

| IMVP_PWRGD | Power supply good signal sent by CPU power supply chip. |

| IMVP_VR_ON | Open CPU power supply. |

| PBAT_PRES# | Detection of insert main battery. |

| SBAT_PRES# | Detection of insert the auxiliary battery. |

| +PBATT | Main battery power supply terminal. |

| +SBATT | Auxiliary/Sub battery power supply terminal. |

| +VCHGR | Charging output voltage. |

| H_RESET# | The North Bridge sent CPU reset signal. |

| H_PWRGOOD | PGD reset signal sent by the South Bridge to CPU. |

| CLK_ENABLE# | The open signal of clock chip: Activelow level. |

| PGD_IN | One of the conditions of that CPU power supply chip sent CLK_EN#, PGOOD and others. |

| +VCCP_1P05VP | The front side bus power supply: 1.05V. |

| SUSPWROK | The reset signal of all SUS power brings together to generate the SUSPWROK signal. |

| RUNPWROK | The PGD signal of all RUN power convergence to this signal. |

| +0.9V_DDR_VTTP | Memory VTT power supply. |

| _VCC_GFX_CORE | The discrete graphic card core power supply. |

| GFX_ON | Open discrete graphics card power supply. |

| RUN_ON | EC sent open S0 state voltage. |

| SUS_ON | After receiving the trigger signal, EC sent SUS_ON to use to open the South Bridge standby power supply and memory main power supply. |

| POWER_SW# | A low voltage signal generated by the power switch or keyboard and EC chip receives this boot signal. |

| ACAV_IN | The Power Adapter detection signal. |

| THERM_STP# | Overheat protection signal; Active-low level. |

| ALWON | EC sent a ALWON signal to the system power supply chip to open/start-up the system power supply. |

| +PWR_SRC | The common point voltage. |

| +DC_IN | Power Adapter voltage input. |

| RTC_CELL | The motherboard button battery voltage. |

Operating Sequence:

Although there are countless motherboard manufacturers, there is a sequence of operation for all of them, which allows us to follow a more direct path to the defect.

Generically speaking, the operating sequence, known as the start sequence, is the definition of the state in which the card is completely off until the moment we turn on and video appears on the screen.

From the moment we connect the charger to the motherboard, several voltages appear, one after the other, which start the sequence of operation (we will address these voltages later).

Following a numerical logic, let's assume that a card connects and displays video with 10 voltages (T1, T2, T3, T4, T5, T6, T7, T8, T9, T10), if for some reason T6 for example, does not appear (any shorted component can cause this), of course the operating sequence will be interrupted and there will also be no voltage after it (T7, T8, T9 and T10).

That is to say in this case that if T5 is present on the board, you do not need to check the voltages prior to it (T1, T2, T3 and T4), as the board only appears if the voltage before it is present.

Did you understand until now? So let's continue.

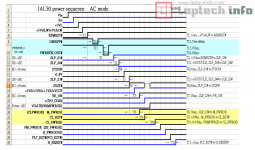

I advise that when you receive a defective laptop, the first thing you do is to understand where that defect is through the symptom. If it is on the motherboard, download the schematic diagram and look for the page of the operating sequence, as the example of the image below (schematic of the motherboard compal LA-4101P, page 5.

The sequence of operation is given from top to bottom as shown by the numerical sequence in the column on the left.

On this page of the schematic diagram you will find the main pulses and voltages for the motherboard to connect (it is important to know that both may have different names depending on the manufacturer's design)

At first glance all these letters and numbers may seem complex, but in reality everything is very easy to understand and for that we will get straight to the point.Note: Pulse is the name given to the exchange of information between certain components of the motherboard (ex: ON/OFF# is the pulse of the power button that will turn the laptop on and off).

In the next lines we will delve into some pulses and voltages of the laptop schematic diagram:

1. Vin, B+: High voltage (originated from the charger).

2. + 3VL: Also known as VREG3. Voltage that rises in the Primary PWM (this is not yet the primary voltage of 3V).

3. +5VALW/+3VALW: The famous primary voltages. They are generated by the Primary PWM and can be measured in their respective inductors, according to the schematic diagram..

4. RSMRST#: Resume and Reset signal, responsible for resetting and making the North or South Bridge ready to work. It must be at a high level (Ex 3V) in stand by and reset to zero when pressing the power button.

5. ON/OFF#: Power button signal, it must be at a high level (usually 3V) in standby, when pressing the button it goes to 0V, making the laptop turn on. Knowing this, you will be able to diagnose a problem in the power button in seconds.

There are many other pulses and voltages that, depending on the design, may vary in name and function. But don't worry, as you study schematics diagram, you will be able to assimilate each one of them and the interpretation will become more and more simple.

As you can see, some voltages appear on the motherboard even before the power button is pressed, that is, they appear on STAND BY (only connected to a charger or battery).

This tension is known as primary. It is from these voltages that all other circuits can be fed. We will understand how they arise and how to diagnose defects in them, from now on.